## Sixth International Workshop on Formal Techniques for Safety-Critical Systems (FTSCS 2018)

Preliminary Proceedings

Editors: Cyrille Artho and Peter Csaba Ölveczky

#### Preface

This volume contains the preliminary proceedings of the Sixth International Workshop on Formal Techniques for Safety-Critical Systems (FTSCS 2018), held in Gold Coast on November 16, 2018, as an ICFEM workshop.

The aim of this workshop is to bring together researchers and engineers who are interested in the application of formal and semi-formal methods to improve the quality of safety-critical computer systems. FTSCS strives to promote research and development of formal methods and tools for industrial applications, and is particularly interested in industrial applications of formal methods. Specific topics include, but are not limited to:

- case studies and experience reports on the use of formal methods for analyzing safety-critical systems, including avionics, automotive, railway, medical, and other kinds of safety-critical and QoS-critical systems;

- methods, techniques and tools to support automated analysis, certification, debugging, etc., of complex safety/QoS-critical systems;

- analysis methods that address the limitations of formal methods in industry (usability, scalability, etc.);

- formal analysis support for modeling languages used in industry, such as AADL, Ptolemy, SysML, SCADE, Modelica, etc.; and

- code generation from validated models.

The workshop received 22 regular paper submissions. Each submission was reviewed by at least three referees. Based on the reviews and extensive discussions, the program committee selected 10 papers for presentation at the workshop and inclusion in this volume. Another highlight of the workshop is an invited talk by César Muñoz on using formal methods for unmanned aerial vehicles at NASA.

Revised versions of accepted papers will appear in the post-proceedings of FTSCS 2018 that will be published as a volume in Springer's Communications in Computer and Information Science (CCIS) series. Extended versions of selected papers from the workshop will also appear in a special issue of the Science of Computer Programming journal.

Many colleagues and friends have contributed to FTSCS 2018. We thank César Muñoz for accepting our invitation to give an invited talk and the authors who submitted their work to FTSCS 2018 and who, through their contributions, make this workshop an interesting event. We are particularly grateful that so many well known researchers agreed to serve on the program committee, and that they provided timely, insightful, and detailed reviews. We also thank the editors of Communications in Computer and Information Science for agreeing to publish the proceedings of FTSCS 2018 as a volume in their series, and Jin Song Dong for his help with the local arrangements.

We hope that you will all enjoy the workshop!

November 2018 Surfers Paradise Cyrille Artho Peter Csaba Ölveczky

### **Table of Contents**

| Keynote                                                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Formal Methods in the Development of Highly Assured Software for Unmanned Aircraft Systems                                            | 1   |

| Session 1: Timing analysis                                                                                                            |     |

| Formal Timing Analysis of Digital Circuits                                                                                            | 2   |

| A benchmarks library for parametric timed model checking Étienne André                                                                | 18  |

| Session 2: Decision, planning, optimization                                                                                           |     |

| Synthesizing and Optimizing FDIR Recovery Strategies From Fault Trees  Liana Mikaelyan, Sascha Müller, Andreas Gerndt and Thomas Noll | 27  |

| Formal Verification of Random Forests in Safety-Critical Applications<br>John Törnblom and Simin Nadjm-Tehrani                        | 44  |

| Modular Verification of Vehicle Platooning with Respect to Decisions,  Space and Time                                                 | 61  |

| Session 3: Refinement                                                                                                                 |     |

| Abstraction Refinement with Path Constraints for 3-Valued Bounded Model Checking                                                      | 78  |

| Refinement of Statecharts with Run-to-Completion Semantics                                                                            | 97  |

| Session 4: Transformation and Analysis                                                                                                |     |

| Model Transformation with Triple Graph Grammars and Non-terminal Symbols                                                              | 114 |

| Embedding CCSL into Dynamic Logic: A Logical Approach for the Verification of CCSL Specifications                                     | 131 |

| Formal Stability Analysis of Control Systems                                                                                          | 149 |

#### **Program Committee**

Étienne André Université Paris 13

Toshiaki Aoki JAIST

Cyrille Valentin Artho KTH Royal Institute of Technology

Kyungmin Bae Pohang University of Science and Technology

Daniel Fava University of Oslo

Sabine Glesner TU Berlin

Osman Hasan National University of Sciences and Technology

Klaus Havelund Jet Propulsion Laboratory

Jérôme Hugues ISAE

Marieke Huisman University of Twente Ralf Huuck UNSW/SYNOPSYS

Fuyuki Ishikawa National Institute of Informatics

Takashi Kitamura National Institute of Advanced Industrial Science

and Technology (AIST)

Thierry Lecomte ClearSy

Yang Liu Nanyang Technological University

Robi Malik University of Waikato

Frédéric Mallet Université Nice Sophia-Antipolis

Roberto Nardone Mediterranean University of Reggio Calabria

Thomas Noll RWTH Aachen University

Peter Csaba Ölveczky University of Oslo

David Pearce Victoria University of Wellington

Markus Roggenbach Swansea University Ralf Sasse ETH Zurich

Martina Seidl Johannes Kepler University Linz Graeme Smith The University of Queensland

Sofiène Tahar Concordia University Carolyn Talcott SRI International Tatsuhiro Tsuchiya Osaka University

Mark Utting University of the Sunshine Coast

András Vörös Budapest University of Technology and Economics

Michael Whalen University of Minnesota Huibiao Zhu East China Normal University

#### **Additional Reviewers**

Elderhalli, Yassmeen Siddique, Umair

## Formal Methods in the Development of Highly Assured Software for Unmanned Aircraft Systems

César Muñoz

NASA Langley Research Center, Hampton, USA

Abstract. Operational requirements of safety-critical systems are often written in restricted specification logics. These restricted logics are amenable to automated analysis techniques such as model-checking, but are not rich enough to express complex requirements of unmanned systems that involve, for example, the physical environment. This talk advocates the use of expressive logics, such as higher-order logic, to specify the complex operational requirements and safety properties of unmanned systems. These rich logics are less amenable to automation and, hence, require the use of interactive theorem proving techniques. However, they enable the formal verification of complex numerically intensive algorithms and the rigorous validation of their implementations. The proposed approach is illustrated with two cases studies from NASA's research on Unmanned Aircraft Systems (UAS): Detect and Avoid Alerting Logic for Unmanned Systems (DAIDALUS) and Independent Configurable Architecture for Reliable Operations of Unmanned Systems (ICAROUS). DAIDALUS is the reference implementation of detect and avoid for UAS in FAA DO-365. ICAROUS is a software architecture built on top of DAIDALUS that enables the development of autonomous UAS applications.

## Formal Timing Analysis of Digital Circuits

Qurat-ul-Ain and Osman Hasan

School of Electrical Engineering and Computer Science (SEECS)

National University of Sciences and Technology (NUST)

Islamabad, Pakistan.

{qain.msee15seecs.osman.hasan}@seecs.nust.edu.pk

Abstract. Formal verification provides complete and sound analysis results and has widely been advocated for the functional verification of digital circuits. Besides the functional verification, a very important aspect of digital circuit design process is their timing analysis. However, despite its importance and critical nature, timing analysis is usually performed using traditional techniques, like gate-level simulation or static timing analysis, which provide approximate results due to their in-exhaustive nature and thus may lead to an undesired functional behavior as well. To overcome these issues, we propose a generic framework to conduct the formal timing analysis using the Uppaal model checker in this paper. The first step in the proposed framework is to represent the timing characteristics of the given digital circuit using a state transition diagram in Uppaal. In this model, delays are integrated using the corresponding technology parameters and the information about timing paths is added using Quratus Prime Pro, which is used as a path extracting tool. The Uppaal timing model is then verified through TCTL properties to obtain timing related information, like maximum delay. For illustration purposes, we present the analysis of a number of real-world digital circuits, like Full Adder, 4-Bit Ripple Carry Adder, Shift Registers as well as C17, S27, S208, and S386 benchmark circuits.

**Keywords:** Timed Automata, Uppaal, Formal Verification, Timing Analysis, Model Checking

#### 1 Introduction

Due to the gradual reduction in transistor sizing governed by the Moore's law and the continuous increase in integrated circuit complexity, modeling and analyzing timing characteristics of digital circuits has become a very challenging task. Timing analysis usually involves determining the timing delays associated with each component of the circuit based on the technology used and its fan-out while considering the circuit variations. The delays of individual components are then used to calculate the overall circuit delay using various analysis techniques, like gate-level simulation [25] or static timing analysis [16]. However, neither of these techniques can ensure an exhaustive analysis due to the complexity of the present-age digital circuits. This kind of an in-exhaustive analysis results in an

incorrect timing analysis, which may in turn lead to a non-optimal design or a functional bug. Digital circuits are increasingly being used in designing safety-critical systems, like the ones used in health-care, transportation and defense related domains. Thus, a non-optimal design or a functional issue may lead to disastrous consequences, like financial losses or even the loss of human life in worst case scenarios.

Formal verification [14] is known to overcome the above-mentioned limitations of traditional analysis approaches, like simulation. It has been extensively used for the functional verification of digital circuits [4, 9, 15, 27]. The main idea in formal verification based analysis is to construct a formal model of the given circuit and formally verify the desired behavior of this model using formal specifications. Model checking [7] is one of the most commonly used formal verification techniques for the functional verification of digital circuits due to its automatic verification and the ability to provide a counterexample in the case of a failing property. It mainly involves modeling the system as a state transition diagram and the verification is done by exhaustively exploring the state space in a push button manner.

Due to the dire need of accurate analysis in the domain of timing analysis, formal verification of timing analysis of digital circuits using model checking got some attention in recent years. The model checker Open-Kronos has been used for the timing analysis of combinational circuits [24]. An abstract model of the given circuit is developed by partitioning the circuit into smaller subcircuits and reachability graphs are used to model timed automata. A major limitation of this approach is that it uses fixed delay values for all the gates, e.g., the delay of an inverter is assumed to be 0, and thus the technology parameters and process variations are completely ignored in the models. Similarly, Open-Kronos is also used for timing analysis with bi-bounded delay values in [8]. Formal timing verification of digital circuits, including their combinational and sequential components, is performed in [5]. The given circuit is modeled at the macroscopic level where a state transition graph (STG) is modeled as a configuration of inputs while excluding the multiple input transitions. The delays of the components are extracted from SPICE simulations. The timing behavior of the SPSMALL memory architecture is verified using a parametric timed automata based model [12]. This technique derives a set of linear constraints that ensure the correctness of the response times of the memory. Similarly, symbolic timing verification of concurrent systems is proposed in [13]. The complex polyhedra modeling approach is used as the abstraction to represent sets of timed states as a timed transition system. Each event in this model has a symbolic delay defined in an interval  $[d_i, D_i]$  where  $d_i$  and  $D_i$  symbolize minimum and maximum delay values, respectively.

Formal timing analysis of digital circuits has also been done with various other motivations. For example, digital circuits have been formally modeled using propagational delays, which are assumed to take values in an interval  $\delta[\tau_{min}, \tau_{max}]$  in the context of testing of circuits in [28]. The model is developed in Uppaal, where delay faults are intentionally inserted into the circuit to gener-

ate counterexamples. These counterexamples are then used for testing of circuits. Similarly, formal timing analysis of combinational circuits has been performed to detect the Hardware Trojans using side channel parameters, like delay and power, in [1]. The main idea in this work is to insert an intrusion in the circuit in the form of logic gates. After intrusion, formal timing verification is performed to generate a counterexample. In this technique, only combinational circuits are formally verified and no sequential circuit is analyzed. Moreover, various circuit paths are identified manually for delay calculations in a circuit in this work [1]. Based on the above-mentioned discussion, we identify the following limitations in the existing literature:

- Incompleteness: The existing timing analysis approaches do not consider all the gates and all their possible input transitions.

- Limited Scope: The delay models used in formal techniques are usually not based on real delay values.

- Inviability: The exhaustive analysis techniques have enormous verification times, which leads to their infeasibility for large circuits.

To overcome the deficiencies of the existing formal timing analysis approaches for digital circuits and thus making the formal timing analysis more accurate, we propose to use the Elmore delay model [30] to compute the delays of both combinational and sequential components of the given circuit. Moreover, instead of using bi-bounded delays, we propose to calculate the value of the delay at every possible input transition of every gate in the design. For example, in the case of a 2 input gate, delays are calculated for all the four possible transitions  $\Gamma_{Delay} = [d_{00}, d_{01}, d_{10}, d_{11}]$ . Moreover, instead of manually searching of timing paths within a circuit as is the case for all existing formal timing analysis approaches, we propose to use the Quartus Prime Pro software [21] for automatically extracting the paths of the given circuit. This choice allows us to not only automate the timing analysis flow but also reduces the risks of ignoring some timing paths in the design. While using the above-mentioned information, we develop a formal model of the given circuit in the Uppaal model checker and then verify its desired timing properties in Uppaal. To facilitate the modeling and verification process, we provide a generic framework in which by knowing delays of the basic circuit blocks, i.e., NAND, NOR, NOT and a Flip-Flop, we can verify the timing behavior of any digital circuit, such as the clock period of a circuit, the critical paths as well as setup and hold time constraints in a circuit. It is important to note that by using a model checking tool for the timing analysis, our results are based on a rigorous exploration of the state space of the circuit model and thus all the paths and input values are implicitly considered in the analysis.

The remainder of the paper is structured as follows: We present a brief introduction about the Uppaal model checker in Section 2. The proposed methodology is explained in detail in Section 3, followed by Section 4 where we describe case studies and verification results. Finally, Section 5 concludes the paper.

4

#### 2 Uppaal Model Checker

Uppaal [6] is a free academic model checker for the formal verification of realtime systems. It is based on the timed automata theory [3] and its modeling language offers many additional features, such as bounded integer variables.

#### 2.1 Timed Automata

A timed automaton (TA) is a tuple  $TA = (S, s_o, T, \sigma, Y, \beta)$ , where:

- S is a set of locations.

- $-s_o \in S$  is an initial location.

- T is a set of clocks.

- $-\sigma$  is a set of all defined actions.

- $-Y \subseteq S \times \sigma \times B(T) \times 2^T \times S$  is a set of edges between locations.

- $-\beta: S \to B(T)$  assigns invariants to locations.

B(T) is the set of conjunctions over simple conditions, i.e.,  $x-y\bowtie c$  or  $x\bowtie c$ , where  $c\in\mathbb{N},\ x,y\in T$  and  $\bowtie\in\{=,\geq,\leq,>,<\}$ . A clock valuation is a function  $u:T\to\mathbb{R}_{\geq 0}$  from the set of clocks to the non-negative real values. Thus, writing  $u\in\beta(s)$  means that u satisfies  $\beta(s)$ . Timed automata are finite state automata having states and transitions, enriched with built-in clocks, which evolve at a uniform rate and can be reset to their initial value.

A state is a pair  $(S, \alpha)$  where  $\alpha$  is a valuation of clocks and variables in that particular state. A state  $(S, \alpha)$  has a discrete transition t, and system moves to the next state  $(S', \alpha')$  if the constraints on t, called guards, are satisfied. The interconnection between two timed automata can be obtained by using synchronization channels. The signal is emitted by one automaton in transition t and received by one or more automata.

#### 2.2 Queries

Verification of a model using the required specifications is a crucial step in modechecking. Similar to a model, properties must be expressed in a formal language. Uppaal uses a simplified version of TCTL (timed computational tree logic) properties. Various path formulae supported by Uppaal are:

- $-\exists \Diamond \rho$  (Possibly): There exists a path along which query  $\rho$  eventually holds.

- $-\exists \Box \rho$  (Potentially always): There exists a path where query  $\rho$  always satisfies.

- ∀□ $\rho$  (Invariantly): For all paths, query  $\rho$  always satisfies .

- $\forall \Diamond \rho$  (Eventually): For all paths, query  $\rho$  eventually satisfies.

- $-\rho \leadsto \xi$  (Leads-to): Whenever  $\rho$  satisfies, query  $\xi$  holds always eventually.

#### 3 Proposed Methodology

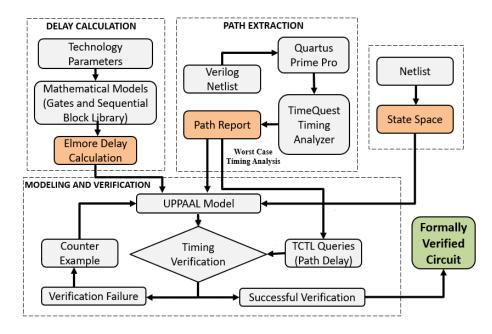

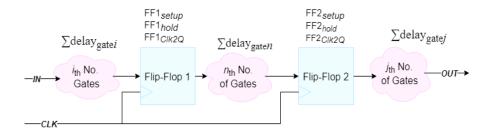

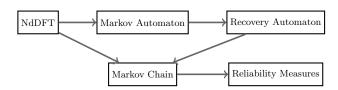

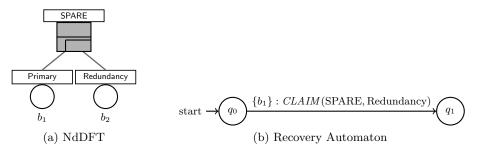

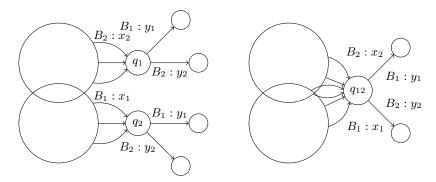

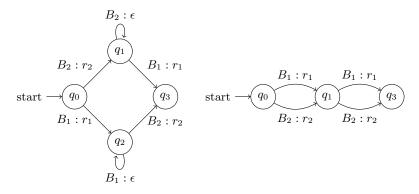

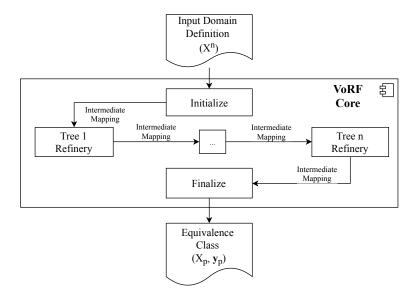

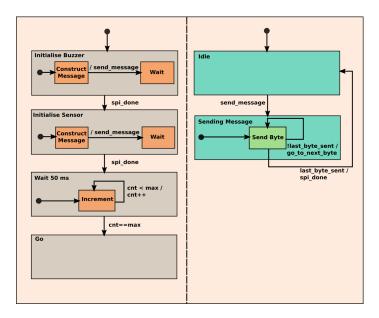

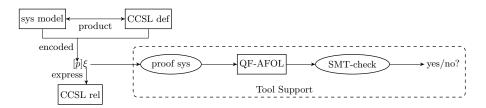

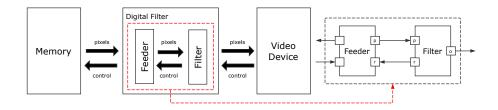

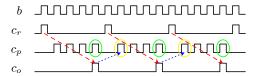

In this section, we explain the proposed methodology, depicted in Figure 1, for the formal timing analysis of a digital circuit. Our methodology is comprised of three major steps: delay calculation, path extraction and modeling and verification in the Uppaal model checker.

Fig. 1. Proposed Methodology

#### 3.1 Delay Calculation

The individual gate delays are estimated in the proposed methodology based on individual transitions at the gate inputs using the Elmore delay model [1], which computes the delay by representing each circuit in the form of an RC tree. Many timing analysis tools estimate the delay of the component based on the time difference between 50% of the input transition to the 50% of the output transition. However, the Elmore delay model considers the Resistor Capacitor relationships to compute the delay and hence provides a better estimate of the delay compared to the above-mentioned traditional approach. The delay is estimated by the model from a source node to one of the leaf nodes by accumulating the capacitances  $C_i$  on each node of the path, multiplied by the effective resistance  $R_{is}$  on the shared path from source node to the leaf node.

$$T_e = \sum_i C_i \times R_{is} \tag{1}$$

$$\tau_{delay} = T_e \times ln(2) \tag{2}$$

Using the basic technology parameters, we calculate the capacitance and resistance values for PMOS and NMOS transistors in an ON state. We propose to develop timing models for the basic circuit components, i.e., NAND, NOR, NOT and a Flip-Flop. These gates are then further used to model complex circuits. Gate capacitances for PMOS and NMOS [22] are given below:

$$C_{qatenMOS} = C_{qminN} \times fan - out \times WR_{nMOS}$$

(3)

$$C_{qatepMOS} = C_{qminP} \times fan - out \times WR_{pMOS} \tag{4}$$

Where  $C_{gmin}$  represents the minimum gate capacitance and WR represents the width ratio.  $C_L$  is the load capacitance calculated from the addition of gate capacitances of all the gates connected at the output of the considered component.

$$C_L = \sum_{k=1}^{a} C_{gatenMOSk} + \sum_{j=1}^{b} C_{gatepMOSj}$$

(5)

Diffusion capacitance  $C_{Diff}$  can be calculated from the drain capacitance [30]. The addition of load and diffusion capacitance leads to the total capacitance of a gate  $C_T$ , which is used for the calculation of delay.

$$C_T = C_L + C_{Diff} (6)$$

Resistance of a PMOS or NMOS [23] can be calculated as follows:

$$R_{on} = \frac{1}{WL \times \mu \times Cox \times (V_{GS} - V_{TH})}$$

(7)

Using the values of corresponding resistances and capacitances, we can find out the Elmore delays for NAND, NOT, and NOR gates. Delay is calculated by considering all the possible input transitions of a gate. For example, the Elmore delay equations for the NAND gate are shown in Table 1.

Table 1. Nand Gate Delay Equations

| Input Transition | Output | Delay Equation                                         |

|------------------|--------|--------------------------------------------------------|

| 00               | 1      | $ln(2) \times [(C_T \times R_p)/(2 \times WR_{pMOS})]$ |

| 01               | 1      | $ln(2) \times [(C_T \times R_p)/WR_{pMOS}]$            |

| 10               | 1      | $ln(2) \times [((C_T + C_{ST}) \times R_p)/WR_{pMOS}]$ |

| 11               | 0      | $ln(2) \times [(C_T \times 2 \times R_n)/WR_{nMOS}]$   |

We have used the True Single-Phase Clocked (TSPC) Flip-Flop model [22] to capture the timing behavior of the Flip-Flop as this provides less complexity and less number of transistors to deal with [22]. Setup time, hold time, and clock to Q delay are the three most important timing constraints in a Flip-Flop. In the TSPC Flip-Flop model, the setup time is assigned a delay of one inverter, the hold time is considered to be less than one inverter delay and the propagational delay is considered to be equal to three inverter delays. Similarly, in our model, we consider the hold time to be equal to one inverter delay in the worst case. The delay equations used in our model for setup time, hold time and the clock to Q in a Flip-Flop are given in Table 2.

#### 3.2 Path Extraction

Calculation of a delay in a circuit, which is composed of several gates and Flip-Flops, is done based on its various paths, i.e., from input to a Flip-Flop, between

Data Input Output Delay Equation Setup Time 0  $ln(2) \times [(C_T \times R_p)/WR_{pMOS})]$ 0 1  $ln(2) \times [(C_T \times R_n)/WR_{nMOS})]$ 1 Hold Time  $ln(2) \times [(C_T \times R_p)/WR_{pMOS})]$ 0 0  $ln(2) \times [(C_T \times R_n)/WR_{nMOS})]$ 1 1 Clk2Q Delay 0 0  $ln(2) \times [(3 \times C_T \times R_p) / WR_{pMOS})$  $[ln(2) \times [(3 \times C_T \times R_n) / WR_{nMOS})]$ 1 1

**Table 2.** Flip-Flop Delay Equations

Flip-Flops and from a Flip-Flop to an output. The delay of a path is calculated by adding delays of logic elements present in that path. In the case of smaller circuits, we can manually analyze all the paths in a circuit and can calculate the delays of all the paths. But in case of large circuits, it is impossible to analyze the paths manually, therefore we propose to use a software that can provide all the valid paths in a circuit automatically from a given circuit netlist. We found Altera Quartus Prime Pro [21] to be the most relevant tool for this purpose. It not only provides all the possible paths from all input ports to all output ports but can also provide paths from the input port to a Flip-Flop, Flip-Flop to a Flip-Flop, or Flip-Flop to an output port.

In the path extraction phase of the proposed methodology, we have to provide the Verilog code of the circuit that needs to be analyzed. This Verilog file is first analyzed and synthesized. After compilation, we run the TimeQuest Timing Analyzer tool to get the information about the paths in the given circuit. Synopsys design constraint file and a timing netlist is thus created automatically by the Timing Analyzer. After this, we can analyze the paths that are reported by the TimeQuest Timing Analyzer.

#### 3.3 Modeling and Verification in Uppaal Model Checker

Modeling and verification in Uppaal is the most important step in our approach for the timing verification of circuits. Firstly, the given netlist is translated to its corresponding state transition diagram. This state transition diagram along with the delay values of logic elements and path information from TimeQuest Timing Analyzer is used for this purpose in the Uppaal Model Checker. The TCTL properties of path delays have to be given to the Uppaal model checker as well. The state space model is then verified in Uppaal against the identified TCTL properties to judge the circuit performance. We mainly check that the delay in a circuit is less than the required maximum delay. If the delay of the circuit exceeds the maximum delay, then the Uppaal model checker returns a counterexample which provides us the exact trace that caused the timing violation. Thereafter,

it can be investigated if the issues are due to a modeling error or its an actual timing violation.

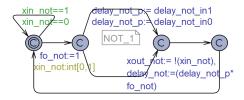

In order to facilitate the modeling of digital circuits, we developed the formal models of the basic gates, i.e., NAND, NOR, NOT and a Flip-Flop, in Uppaal and these models can be built upon to formalize models of larger complex circuits. For example, The TA of the NOT gate is shown in Figure 2 where  $xin\_not$  is the input and  $xout\_not$  is the output. At the initial state, the selection expression  $xin\_not$ : int[0, 1] allows to assign a boolean value 1 or 0 to the input  $xin\_not$ . The fan-out  $fo\_not$  is updated depending upon how many gates are connected at the output port of the gate. Based on the value of the input, internal resistances, internal capacitances, fan-out, and various technology parameters, the delay  $delay\_not$  is calculated using the Elmore delay equation. The output gets its appropriate value, i.e., the negation of input  $out\_not := !(xin\_not)$ , after the delay has elapsed. Similarly, the models of other basic gates have also been developed and they can be used to formalize any combinational gate-level circuit. Sequential circuits also contain Flip-Flops besides the basic logic gates

Fig. 2. Timed Automaton of the NOT Gate

Fig. 3. Timed Automata of a Flip-Flop and a Clock

and to formalize their behavior, we also formalized the Flip-Flop. The proposed Flip-Flop model along with the clock is shown in Figure 3. The input signal is updated in the first state. Based on the value of the input, internal resistances, internal capacitances, fan-out, and various technology parameters, the setup time, hold time and clock to Q delay is calculated using the Elmore delay equations.

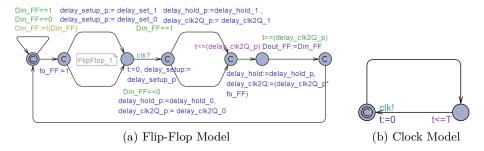

In the proposed methodology, we can develop the models of more complex circuits by interconnecting the basic gates and Flip-Flop models. Some simple circuits designed from the basic gates, i.e., NAND, NOT, and NOR, are shown in Figure 4.

Fig. 4. Designing Some Simple Circuits Using Basic Gates

We propose to verify the following properties.

- Firstly, we check the deadlock property, which ensures that the timed automaton is not stuck at any particular state and thus moves ahead through all the states.

$$\forall \Box not deadlock$$

- For verifying combinational circuits, we check that the delay, considering all the paths delay in the given combinational model, does not exceed the maximum delay value for the given circuit. If the delay exceeds the maximum value and the property fails then we get a counterexample.

$$\forall \Box !((delay_{qate1} + delay_{qate2} + \cdots + delay_{qaten}) > D \max_{comb}))$$

Where  $D \max_{comb} = \max(delay_{gate1}, delay_{gate2}, \cdots, delay_{gaten})$  represents the maximum delay in the considered path.

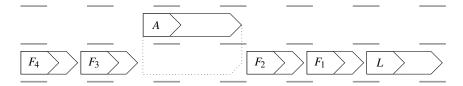

For verifying sequential circuits, we check the input port to Flip-Flop and Flip-Flop to output port paths just like we check the timing properties of combinational circuits. Moreover, we also need to conduct the Flip-Flop to Flip-Flop path analysis while considering the setup and hold time constraints, which allows us to determine the clock period of the given circuit and avoid metastability. For example, consider a typical sequential circuit scenario, shown in Figure 5, where we have an input port IN, two Flip-Flops FF1 and FF2 and an output port OUT. There are i gates between input

#### Q. U. Ain and O. Hasan

10

Fig. 5. A Typical Sequential Circuit

and FF1, n gates between Flip-Flops, and j gates between FF2 and output. We propose to verify the following properties in this case.

$$\forall \; \Box \; ((delay_{gate1} + delay_{gate2} + \cdots + delay_{gatei}) \leq D \max_{INtoFF})$$

$$\forall \; \Box \; (T \geq (FF1_{clk2Q} + delay_{gate1} + delay_{gate2} + \cdots + delay_{gaten}) + FF2_{setup})$$

$$\forall \; \Box \; ((FF1_{clk2Q} + delay_{gate1} + delay_{gate2} + \cdots + delay_{gaten}) \geq FF2_{hold})$$

$$\forall \; \Box \; ((FF2_{clk2Q} + delay_{gate1} + delay_{gate2} + \cdots + delay_{gatej}) \leq D \max_{FFtoOUT})$$

#### 4 Case Studies

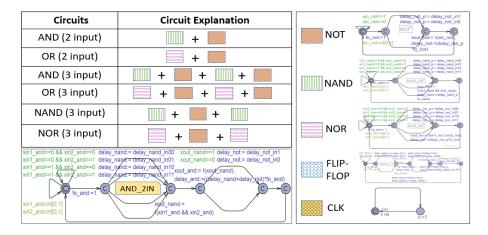

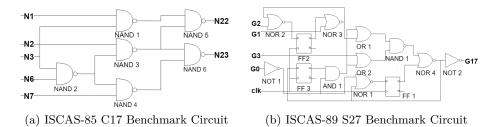

Fig. 6. Benchmark Circuits

For illustration purpose, we present the analysis of C17, and S27 benchmark circuits in this section. Due to the large size of transition diagrams, we only summarize path information and verified properties of these circuits in this section.

#### 4.1 C17 Benchmark

C17, shown in Figure 6(a), is one of the benchmarks from ISCAS-85 that consists of 5 input ports and 2 output ports. The path report of the C17 circuit generated from TimeQuest Timing Analyzer is modeled in Uppaal with the help of a single function in order to reduce the complexity in a state transition diagram.

```

c17_p1 = (delay1_nand_c17+delay5_nand_c17); //N1 --> N22

c17_p2 = (delay3_nand_c17+delay5_nand_c17); //N2 --> N22

c17_p3 = (delay3_nand_c17+delay6_nand_c17); //N2 --> N23

c17_p4 = (delay2_nand_c17+delay3_nand_c17+delay6_nand_c17); //N3 --> N23

c17_p5 = (delay2_nand_c17+delay3_nand_c17+delay5_nand_c17); //N3 --> N22

c17_p6 = (delay2_nand_c17+delay3_nand_c17+delay5_nand_c17); //N6 --> N23

c17_p7 = (delay2_nand_c17+delay4_nand_c17+delay5_nand_c17); //N6 --> N23

c17_p8 = (delay4_nand_c17+delay6_nand_c17); //N7 --> N23

c17_p9 = (delay1_nand_c17+delay5_nand_c17); //N3 --> N22

c17_p10 = (delay2_nand_c17+delay5_nand_c17); //N3 --> N23

c17_p10 = (delay2_nand_c17+delay5_nand_c17); //N3 --> N23

c17_p11 = (delay2_nand_c17+delay4_nand_c17+delay6_nand_c17); //N3 --> N23

```

Some of the properties that are verified against specified paths are shown below, where Tmax represents the maximum value of delay for a particular path. These properties are checked against all the paths and all the states in the model.

```

- \ \forall \ \Box \ (!(c17_{p1} > Tmax_{c17-p1})) \qquad \qquad - \ \forall \ \Box \ (!(c17_{p2} > Tmax_{c17-p2}))

```

We also verified many other properties for this benchmark and the details can be found in [2].

#### 4.2 S27 Benchmark

S27, shown in Figure 6(b), is one of the sequential circuit benchmarks from ISCAS-89 that consists of 4 input ports and 1 output port. All the timing reports of S27, including the paths from input to Flip-Flops, between Flip-Flops, and from Flip-Flops to output, generated from TimeQuest Timing Analyzer, were modeled in Uppaal with the help of three functions, one function for each type, in order to reduce the complexity in the resulting state transition diagram.

Some of the properties which are verified against each specified path are written below. We also verified many other properties for this benchmark and the details can be found in [2]. In these properties, the variable, Tmax, represents the maximum delay time and  $T_{clk}$ , represents the time period of a clock.

```

\begin{array}{lll} - \ \forall \ \Box \ (delay_{p1-in} \leq Tmax_{p1-in}) & - \ \forall \ \Box \ (delay_{p2-in} \leq Tmax_{p2-in}) \\ - \ \forall \ \Box \ (T_{clk} \geq (delay_{p1-ff})) & - \ \forall \ \Box \ (T_{clk} \geq (delay_{p2-ff})) \\ - \ \forall \ \Box \ (delay_{p-h1} \geq (delay_{3-hold})) & - \ \forall \ \Box \ (delay_{p-h2} \geq (delay_{3-hold})) \\ - \ \forall \ \Box \ (delay_{p1-out} \leq (Tmax_{p1-out})) & - \ \forall \ \Box \ (delay_{p2-out} \leq (Tmax_{p2-out})) \end{array}

```

#### 4.3 Verification Results

The considered combinational circuits and their verification statistics are summarized in Table 3 using the information about the total number of gates in the given circuit, its verification time and the memory utilization during the verification phase of corresponding circuit. Modeling and verification details of

|                 | 37 1 | C ( | ٠.  | * 7      | 10          |

|-----------------|------|-----|-----|----------|-------------|

| Circuits        | Numb |     |     |          | rification  |

|                 | NAND | NOR | NOT | Time (s) | Memory (MB) |

| C17 [11]        | 6    | -   | -   | 0.014    | 7.34        |

| C17 [29]        | 7    | -   | -   | 0.021    | 7.35        |

| C17 [19]        | 9    | 1   | 2   | 0.033    | 11.78       |

| Full Adder [20] | 11   | -   | -   | 0.032    | 8.82        |

| Full Adder [17] | 10   | 3   | 1   | 0.074    | 16.06       |

| Full Adder [1]  | 14   | 3   | 1   | 0.91     | 18.06       |

| 4-bit RCA [17]  | 40   | 12  | 4   | 63.31    | 2684        |

Table 3. Result of Combinational Circuits

sequential circuits are summarized in Table 4 using the total number of gates and Flip-Flops in the given circuit, its verification time, and the memory utilization. We noticed that the number of explored states during the verification

| Circuits                        | Number of Gates |     | Number of | Verification |          |        |

|---------------------------------|-----------------|-----|-----------|--------------|----------|--------|

| Circuits                        | NAND            | NOR | NOT       | Flip-Flops   | Time (s) | Memory |

|                                 | IIAND           | NOI | NOI       |              | Time (s) | (MB)   |

| Flip-Flop [22]                  | -               | -   | -         | 1            | 0.019    | 7.85   |

| 16-bit SIPO Shift Register [18] | -               | -   | -         | 16           | 0.031    | 10.38  |

| 64-bit SISO Shift Register [18] | -               | -   | -         | 64           | 0.047    | 16.80  |

| 64-bit Ring Counter [26]        | -               | -   | -         | 64           | 0.090    | 21.19  |

| 64-bit Johnson Counter [26]     | -               | -   | 1         | 64           | 0.100    | 27.29  |

| S27 [10]                        | 2               | 6   | 5         | 3            | 2.46     | 43.96  |

| S208 [10]                       | 39              | 37  | 90        | 8            | 316      | 8820   |

| S386 [10]                       | 151             | 36  | 228       | 6            | 3306     | 29745  |

Table 4. Result of Sequential Circuits

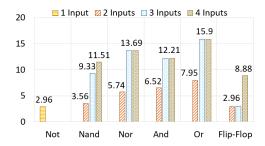

significantly increases with an increase in the number of inputs of basic gates, such as NOT, NAND, NOR, AND and OR. For example, the total number of

Fig. 7. Maximum Delays of Basic Gates

explored states in the 4-bit RCA is 16316416 whereas 105735463 states were explored while analyzing the S368 circuit.

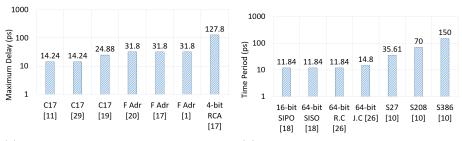

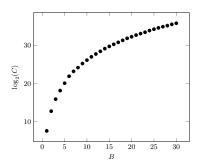

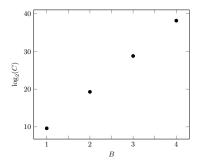

We calculated the maximum delays of basic gates, such as NOT, NAND, NOR, AND and OR as shown in Figure 7. In case of NOT, AND and OR, the maximum delay for 3 input and 4 input is same since the type and number of logic elements are same in a path. The maximum delays in case of the considered combinational circuits is shown in Figure 8(a), whereas the maximum time periods of the clock in case of sequential circuits is shown Figure 8(b).

(a) Maximum Delay in Combinational Cir- (b) Maximum Time Period in Sequential cuits Circuits

Fig. 8. Timing Analysis Results

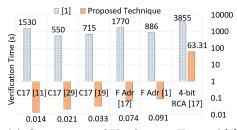

In comparison with an existing technique, presented in [1], which uses the nuXmv model checker for verifying combinational circuits, we find our results to be acquired in a much faster manner as shown in Figure 9(a). This result is based on the maximum time utilized by the model checker for the property verification. For example, the verification time in [1] and the proposed technique in case of the C17 circuit is 1530 s and 0.014 s, respectively. In [1], real numbers are used for modeling and delay calculations, which causes an enormous increase in the state space. We propose to overcome these limitations by performing major real number calculations manually and then use the final delay values in an integral form in the model checker in order to minimize the state explosion problem.

#### 14 Q. U. Ain and O. Hasan

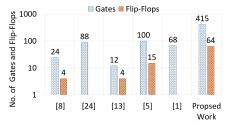

In comparison with the existing techniques, we also verify circuits with larger number of gates and Flip-Flops, i.e., upto 415 gates and 64 Flip-Flops, as shown in Figure 9(b).

- (a) Comparison of Verification Time of [1] and the Proposed Technique

- (b) Number of Logic Elements Analyzed by Existing and Proposed Techniques

Fig. 9. Comparison with Existing Techniques

A summary of comparison of the proposed approach with some existing techniques is shown in Table 5. The comparative analysis is mainly based on seven parameters. The first two parameters show the type of a circuit, which is analyzed, i.e, combinational or sequential circuit. Automatic path extraction, depicts whether the existing techniques perform path analysis automatically or not. Next two parameters refer to delay modeling techniques and the model checker used for the formal verification. Finally, the last two parameters show the maximum gates and Flip-Flops verified by the corresponding technique. Our technique is found to be better than existing techniques in the following ways:

- Unlike some existing techniques [24], [1], we perform timing verification of the combinational as well as sequential circuits.

- In order to perform more realistic modeling and verification, we proposed to use the Elmore delay modeling technique [1] instead of assumed delay model as used in [8], [13], [24], [28].

- We proposed to extract the path information automatically using Quartus Prime Pro [21].

- We verify circuits with comparatively larger number of gates and Flip-Flops compared to all the existing formal timing analysis works.

#### 5 Conclusions

This paper presented a model checking based approach for the formal timing analysis of digital circuits. The main idea behind this approach is to use timed automata as a state transitions diagram for formal modeling of the digital circuits and TCTL queries for the formal verification of their timing properties using the Uppaal model checker. We have developed a generic framework to facilitate the

Delay Max Max Comb Seq Auto. Related Work Tool cctcct Path Model Gates FFAssumed delay Bozga et al. [8] Open-Kronos  $\overline{24}$  $\checkmark$ 4 Х 88 Salah et al. [24] х х Assumed delay Open-Kronos х Clariso et al. [13] Symbolic delay 12 x Abstract Algorithm 4 Bara et al. [5] Spice delay Kronos/ Uppaal 100 15  $\checkmark$ Х Abbasi et al. [1] Elmore delay nuXmv 68  $\mathbf{x}$ X  $\mathbf{x}$ Proposed work Elmore delay Uppaal 415 64

Table 5. Comparison with Existing Techniques

formal timing analysis by developing the models of the basic components of a digital circuit, i.e., logic gates and Flip-Flops, that can be built upon for the formal modeling of more complex circuits. Moreover, the proposed approach supports the automatic path extraction using Quartus Prime Pro along with the modeling and verification in Uppaal. The proposed approach can be used to formally verify various timing characteristics, such as finding the clock period of a circuit, finding the critical path and the setup and hold time constraints in a circuit. For illustration purposes, we used the proposed approach to conduct the formal timing analysis of a number of real-world digital circuits, such as Adders, Shift Registers, C17, S27, S208, and S386 circuits. In the future, we plan to incorporate routing delays and clock skew in a circuit so that we have a more accurate and realistic timing model.

#### References

- Abbasi, I.H., Lodhi, F.K., Kamboh, A.M., Hasan, O.: Formal verification of gatelevel multiple side channel parameters to detect hardware trojans. In: Formal Techniques for Safety-Critical Systems. pp. 75–92. CCIS, vol. 694, Springer (2016)

- 2. ul Ain, Q.: Formal Timing Analysis of Digital Circuits. Available online: http://save.seecs.nust.edu.pk/projects/ftadc/ (2018)

- 3. Alur, R., Courcoubetis, C., Dill, D.: Model-checking for real-time systems. In: Logic in Computer Science. pp. 414–425. IEEE (1990)

- Andraus, Z.S., Sakallah, K.A.: Automatic abstraction and verification of verilog models. In: Proceedings. 41st Design Automation Conference, 2004. pp. 218–223 (2004)

- Bara, A., Bazargan-Sabet, P., Chevallier, R., Ledu, D., Encrenaz, E., Renault, P.: Formal verification of timed VHDL programs. In: Forum on Specification Design Languages. pp. 80–85. IET (2010)

- 6. Behrmann, G., David, A., Larsen, K.G.: A tutorial on Uppaal 4.0 (2006)

- 7. Bérard, B., Bidoit, M., Finkel, A., Laroussinie, F., Petit, A., Petrucci, L., Schnoebelen, P.: Systems and software verification: model-checking techniques and tools. Springer Science & Business Media (2013)

- 8. Bozga, M., Jianmin, H., Maler, O., Yovine, S.: Verification of asynchronous circuits using timed automata. Electronic Notes in Theoretical Computer Science **65**(6), 47–59 (2002)

- 9. Braibant, T.: Coquet: a coq library for verifying hardware. In: International Conference on Certified Programs and Proofs. pp. 330–345. Springer (2011)

- Brglez, F., Bryan, D., Kozminski, K.: Notes on the ISCAS'89 benchmark circuits. North-Carolina State University (1989)

- 11. Bryan, D.: The ISCAS'85 benchmark circuits and netlist format. North Carolina State University 25 (1985)

- 12. Chevallier, R., Encrenaz-Tiphene, E., Fribourg, L., Xu, W.: Timed verification of the generic architecture of a memory circuit using parametric timed automata. Formal Methods in System Design **34**(1), 59–81 (2009)

- 13. Clarisó, R., Cortadella, J.: Verification of timed circuits with symbolic delays. In: Asia and South Pacific Design Automation Conference. pp. 628–633. IEEE (2004)

- Hasan, O., Tahar, S.: Formal verification methods. In: Encyclopedia of Information Science and Technology, Third Edition, pp. 7162–7170. IGI Global (2015)

- 15. Irfan, A., Cimatti, A., Griggio, A., Roveri, M., Sebastiani, R.: Verilog2SMV: A tool for word-level verification. In: Design Automation Test in Europe Conference Exhibition. pp. 1156–1159 (2016)

- 16. Kilts, S.: Static timing analysis. Advanced FPGA Design: Architecture, Implementation, and Optimization pp. 269–278 (2007)

- 17. Mano, M.M., Kime, C.R.: Logic and computer design fundamentals, vol. 3. Prentice Hall (2008)

- 18. Maxfield, C.: Bebop to the Boolean boogie: an unconventional guide to electronics. Newnes (2008)

- 19. Mukhopadhyay, D., Chakraborty, R.S.: Hardware security: Design, threats, and safeguards. Chapman and Hall/CRC (2014)

- Patterson, D.A., Hennessy, J.L.: Computer organization and design. zadnje izdanje (1994)

- 21. Quartus prime standard edition handbook (2015)

- 22. Rabaey, J.M., Chandrakasan, A.P., Nikolic, B.: Digital integrated circuits, vol. 2. Prentice hall Englewood Cliffs (2002)

- 23. Razavi, B.: Design of Analog CMOS Integrated Circuits. Tata McGraw-Hill Education (2002)

- Salah, R.B., Bozga, M., Maler, O.: On timing analysis of combinational circuits.

In: International Conference on Formal Modeling and Analysis of Timed Systems.

pp. 204–218. LNCS, vol. 2791, Springer (2003)

- 25. Saleh, R., Jou, S.J., Newton, A.R.: Gate-level simulation. In: Mixed-Mode Simulation and Analog Multilevel Simulation, pp. 123–152. Springer (1994)

- Shift Registers and Counters. Available online: https://computing.ece.vt.edu/LiaB/Microelectronic%20Systems/Lectures/Digital%20Logic/pdf/Shift%20registers.pdf (2014)

- 27. Shiraz, S., Hasan, O.: A library for combinational circuit verification using the hol theorem prover. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems **37**(2), 512–516 (2018)

- 28. Takan, S., Guler, B., Ayav, T.: Model checker-based delay fault testing of sequential circuits. In: Architecture of Computing Systems. pp. 1–7. VDE (2015)

- Wei, S., Meguerdichian, S., Potkonjak, M.: Malicious circuitry detection using thermal conditioning. IEEE Transactions on Information Forensics and Security 6(3), 1136–1145 (2011)

- Weste, N.H., Harris, D.: CMOS VLSI design: A circuits and systems perspective. Pearson Education India (2015)

# A benchmarks library for parametric timed model checking\*

#### Étienne André

Université Paris 13, LIPN, CNRS, UMR 7030, F-93430, Villetaneuse, France

JFLI, CNRS, Tokyo, Japan

National Institute of Informatics, Japan

Abstract. Verification of real-time systems involving hard timing constraints and concurrency is of utmost importance. Parametric timed model checking allows for formal verification in the presence of unknown timing constants or uncertainty (e.g., imprecision for periods). With the recent development of several techniques and tools to improve the efficiency of parametric timed model checking, there is a growing need for proper benchmarks to test and compare fairly these tools. We present here a benchmarks library for parametric timed model checking made of benchmarks accumulated over the years. Our benchmarks include academic benchmarks, industrial case studies and examples unsolvable using existing techniques.

#### 1 Introduction

Verification of real-time systems involving hard timing constraints and concurrency is of utmost importance, and is now recognized in standards such as the DO-178C, that allows formal methods without addressing specific process requirements. Model checking is a popular model-based technique that formally verifies whether a model satisfies a property. Parametric timed model checking significantly enhances model checking by allowing its application earlier in the design phase, when timing constants may not be known yet. In addition, it is possible to verify systems in the presence of uncertainty, e.g., when some periods are known with some limited precision. This is the case of Thales' FMTV<sup>4</sup> challenge 2014 where the system was characterized with uncertain but constant periods, that rules out the use of non-parametric timed model checking.

Popular formalism for parametric timed model checking include parametric timed automata (PTAs) [3] and parametric time Petri nets [41].

Several tools support parameters, such as HyTech [26] (parametric hybrid automata), Romeo [34] (parametric time Petri nets), IMITATOR [9] (parametric

<sup>\*</sup> This work is partially supported by the ANR national research program PACS (ANR-14-CE28-0002) and by ERATO HASUO Metamathematics for Systems Design Project (No. JPMJER1603), JST.

<sup>&</sup>lt;sup>4</sup> "Formal Methods for Timing Verification Challenge", in the WATERS workshop: http://waters2015.inria.fr/

timed automata), PSyHCoS [14] (parametric stateful timed CSP), or Symrob (robustness for timed automata) [38]. In addition, several tools support the larger class of hybrid automata, such as PHAVer [24] or SpaceEx [25] and, while not explicitly supporting parameters, can encode them.<sup>5</sup> Recently, a growing number of analyses and techniques were proposed to analyze parametric timed models (mainly PTAs) such as SMT-based techniques [31], integer hull abstractions [30], corner-point abstractions [15], distributed verification [8], NDFS-based synthesis [36], machine learning [13,33], etc. However, despite some case studies informally shared between these works, there is a lack of a common basis to compare new tools and techniques in a fair manner. Without a stable list of benchmarks publicly available, it is difficult to assess the efficiency of a new algorithm.

Contribution. We present here a benchmarks library containing academic and industrial case studies collected in the past few years from academic papers and industrial collaborations. In addition, a focus is made on (possibly toy) examples known to be unsolvable using current state-of-the-art techniques, with the hope to encourage the development of new techniques to solve them. Benchmarks are available online in the IMITATOR input format, and distributed using the GNU General Public License.

Related libraries. The library most related to ours is that by Chen et al., that proposes a suite of benchmarks for hybrid systems [18]. However, it aims at analyzing hybrid systems, which are strictly more expressive than PTAs in theory, and incomparable in practice, as most hybrid systems do not feature timing parameters. In addition, that library focuses only on reachability properties. Finally and most importantly, it does not focus on parameters, and the benchmarks are non-parametric. In contrast, our library focuses on parametric timed benchmarks, with various types of properties.

Another interesting library is that by Hoxha, Abbas, and Fainekos [27], that offers Matlab/Simulink models of automotive systems. However, it does not aim specifically at parametric timed model checking; two of our benchmarks originally partially come from the aforementioned library [27].

#### 2 IMITATOR parametric timed automata

Parametric timed automata extend finite-state automata with clocks, i. e., real-valued variables evolving at the same rate. Clocks can be reset along transitions, and can be compared to constants or parameters (integer- or rational-valued) along transitions ("guards") or in locations ("invariants"). IMITATOR parametric timed automata extend PTAs [3] with some useful features such as synchronization between components, stopwatches (i. e., the ability to stop the elapsing of some clocks [17]), presence of parametric linear terms in guards, invariants and resets, shared global rational-valued variables, etc.

<sup>&</sup>lt;sup>5</sup> In a hybrid automaton, a parameter is a variable that can evolve for an arbitrary amount of time at rate 1, and is then "frozen" (rate 0).

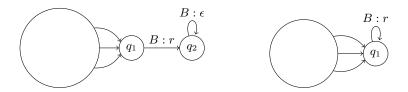

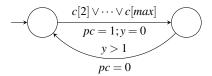

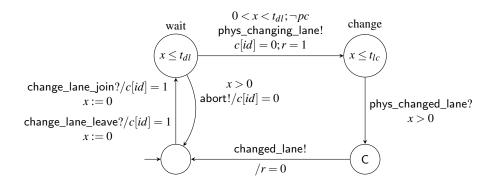

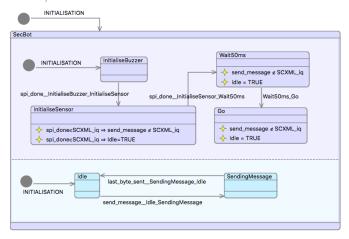

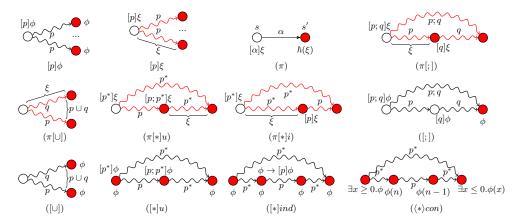

Fig. 1: Examples of PTAs.

Example 1. Consider the PTA in Fig. 1a, containing two locations  $l_0$  and  $l_1$ , two clocks x and y, and one parameter p. The self-loop on  $l_0$  can be taken whenever x=p holds, and resets x, i.e., can be taken every p time units. In addition, initially, as x=y=0 and clocks evolve at the same rate, the transition guarded by  $y=1 \land x=0$  cannot be taken. Observe that, if p=1, then the transition to  $l_1$  can be taken after exactly one loop on  $l_0$ . If  $p=\frac{1}{2}$ , then the transition to  $l_1$  can be taken after exactly two loops. In fact, the set of valuations for which  $l_1$  is reachable is exactly  $\{i \mid i=\frac{1}{n}, n>0 \land n\in \mathbb{N}\}$ .

L/U-PTAs. Lower-bound/upper-bound parametric timed automata (L/U-PTAs) [28] restrict the use of parameters: parameters must be partitioned between lower-bound parameters (always compared with clocks as lower bounds, i.e.,  $p \leq x$  or p < x) and upper-bound parameters. L/U-PTAs enjoy monotonicity properties and, while the full class of PTAs is highly undecidable [5], L/U-PTAs enjoy some decidability results [28,16,12]. U-PTAs [16,11] are L/U-PTAs with only upper-bound parameters.

#### 3 The benchmarks library

#### 3.1 Categories

Our benchmarks are classified into three main categories:

- 1. academic benchmarks, studied in a range of papers: a typical example is the Fischer mutual exclusion protocol;

- 2. industrial case studies, which correspond to a concrete problem solved (or not) in an industrial environment;

- 3. examples famous for being unsolvable using state-of-the-art techniques; for some of them, a solution may be computed by hand, but existing automated techniques are not capable of computing it. This is the case of the PTA in Fig. 1a, as a human can very easily solve it, while (to the best of our knowledge) no tool is able to compute this result automatically.

Remark 1. Our library contains a fourth category: education benchmarks, that consist of generally simple case studies that can be used for *teaching*. This category contains toy examples such as coffee machines. We omit this category from this paper as these benchmarks generally have a limited interest performance wise.

The domain of the benchmarks are hardware asynchronous circuits, communication or mutual exclusion protocols, real-time systems ("RTS") and schedulability problems, parametric timed pattern matching ("PTPM"), train-gate-controllers models ("TGC"), etc.

In addition, we use the following classification criteria:

- number of variables: clocks, parameters, locations, automata;

- whether the benchmark (in the provided version) is easily scalable, i.e., whether one can generate a large number of instances; for example, protocols often depend on the number of participants, and can therefore be scaled accordingly;

- presence of shared rational-valued variables;

- presence of stopwatches;

- presence of location invariants, as some works (e.g., [3,11]) exclude them;

- whether the benchmark meets the L/U assumption.

#### 3.2 Properties

We consider the three following main properties:

reachability / safety: synthesize parameter valuations for which a given state of the system (generally a location, but possibly a constraint on variables) must be reachable / avoided (see e. g., [30]).

**optimal reachability:** same as reachability, but with an optimization criterion: some parameters (or the time) should be minimized or maximized.

unavoidability: synthesize parameter valuations for which all runs must always eventually reach a given state (see e.g., [30]).

**robustness:** synthesize parameter valuations preserving the discrete behavior (untimed language) w.r.t. to a given valuation (see e. g., [7,38]).

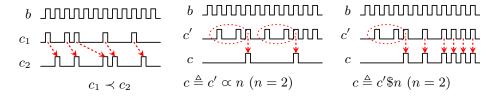

In addition, we include some recent case studies of parametric timed pattern matching ("PTPM" hereafter), i.e., being able to decide for which part of a log and for which values of parameters does a parametric property holds on that log [10]. Finally, a few more case studies have *ad-hoc* properties (liveness, properties expressed using observers [2,4], etc.), denoted "Misc." later on.

#### 3.3 Presentation

The benchmarks library comes in the form of a Web page that classifies models that can be found directly in the IMITATOR repository on Github<sup>6</sup>. The library is available at https://www.imitator.fr/library.html.

The library is made of a list of a set of *benchmarks*. Each benchmark may have different *models*: for example, Flip-flop comes with three models, one with 2 parameters, one with 5, and one with 12 parameters. Similarly, some

$<sup>^{6} \ \</sup>mathtt{https://github.com/imitator-model-checker/imitator/tree/master/} \\ \mathtt{benchmarks}$

Fischer benchmarks come with several models, each of them corresponding to a different number of processes. Finally, each model comes with one or more *properties*. For example, for Fischer, one can either run safety synthesis, or evaluate the robustness of a given reference parameter valuation.

The first version of the library contains 34 benchmarks with 80 different models and 122 properties.

#### 3.4 Performance

We present a selection of the library in Table 1. Not all benchmarks are given; in addition, most benchmarks come with several models and several properties, omitted here for space concern. We give from left to right the number of automata, of clocks, of parameters, of discrete variables, whether the model is an L/U-PTA, a U-PTA or a regular PTA, whether it features invariants and stopwatches, the kind of property, and a computation time on an Intel i7-7500U CPU @ 2.70GHz with 8 GiB running Linux Mint 18.

T.O. denotes time-out (after 300 s). ? denotes unsolvable, because no such algorithm is implemented in existing tools. HS denotes time-out but human-solvable: e.g., for Fischer, one knows the correctness constraint independently of the number of processes, but tools may fail to compute it. This is also the case of the toy PTAs in Figs. 1a and 1b.

Despite time-out, some case studies come with a partial result: either because IMITATOR is running reachability-synthesis ("EFsynth" [30]) which can output a partial result when interrupted before completion, or because some other methods can output some valuations. For example, for ProdCons, IMITATOR is unable to synthesize a constraint; however, in the original work [31], some punctual valuations (non-symbolic) are given.

Robustness case studies are not part of Table 1, but are included in the online library.

#### 4 Perspectives

Syntax. So far, all benchmarks use the IMITATOR input format; in addition, only if the benchmark comes from another model checker (e.g., a HYTECH or UPPAAL model), it also comes with its native syntax. In a near future, we plan to propose a translation to UPPAAL timed automata; however, some information will be lost as UPPAAL does not allow parameters, and supports stopwatches in a limited manner. A future work will be to propose other syntaxes, or a normalized syntax for parametric timed model checking benchmarks.

Contributions and versioning. The library is aimed at being enriched with future benchmarks. Furthermore, it is collaborative, and is open to any willing contributor. A versioning system will be set up with the addition (or modification) of benchmarks in the future.

**Table 1:** A selection from the benchmarks library

| Benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| And-Or   [20]   Circuit   ×   4   4   12   0   −   √   ×   Misc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | enchmark 1    |

| CSMA/CD   [32]   Protocol   √   3   3   3   0   −                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

| Fischer-AHV93 [3] Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | And-Or        |

| Fischer-HRSV02:3 [28] Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CSMA/CD [     |

| Flip-flop:2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | cher-AHV93    |

| Flip-flop:12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ner-HRSV02:3  |

| idle-time-sched:3   35   RTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ip-flop:2     |

| idle-time-sched:5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ip-flop:12    |

| Jobshop:3-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | time-sched:3  |

| Jobshop:4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | time-sched:5  |

| NP-FPS-3tasks:50-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bshop:3-4     |

| NP-FPS-3tasks:100-2         [29]         RTS         ×         4         6         2         0         -         √         ×         Safety         6           SSLAF14-1         [37,40]         RTS         ×         7         16         2         2         -         √         ✓         Safety           SSLAF14-2         [42,40]         RTS         ×         6         14         2         4         -         √         ✓         Safety         ✓           ProdCons: 2-3         [31]         Prodcons.         √         5         5         6         0         L/U         ✓         ×         Safety         ✓           train-AHV93         [3]         TGC         ×         3         3         6         0         L/U         ×         ×         Safety         ✓           WFAS         [15]         Protocol         ×         3         4         2         0         -         √         ×         Safety         ✓           uses         Industrial         Industrial         Industrial         Industrial         Industrial         Industrial         Industrial         Industrial         Industrial         Industrial | bshop:4-4     |

| NP-FPS-3tasks:100-2         [29]         RTS         ×         4         6         2         0         -         √         ×         Safety         6           SSLAF14-1         [37,40]         RTS         ×         7         16         2         2         -         √         ✓         Safety           SSLAF14-2         [42,40]         RTS         ×         6         14         2         4         -         √         ✓         Safety         ✓           ProdCons: 2-3         [31]         Prodcons.         √         5         5         6         0         L/U         ✓         ×         Safety         ✓           train-AHV93         [3]         TGC         ×         3         3         6         0         L/U         ×         ×         Safety         ✓           WFAS         [15]         Protocol         ×         3         4         2         0         -         √         ×         Safety         ✓           uses         Industrial         Industrial         Industrial         Industrial         Industrial         Industrial         Industrial         Industrial         Industrial         Industrial | S-3tasks:50-0 |

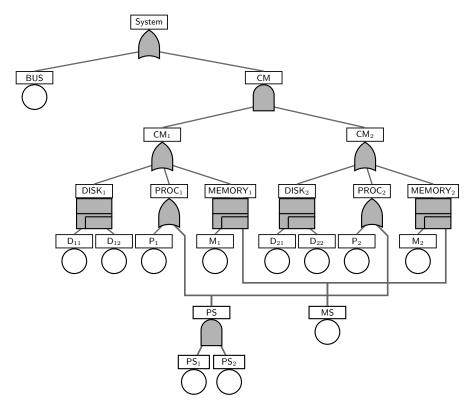

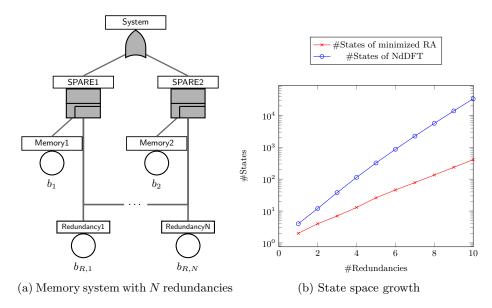

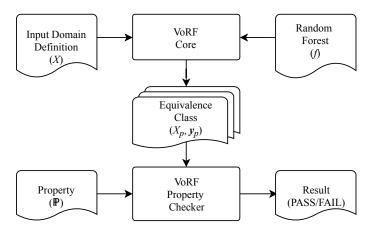

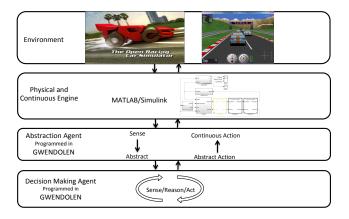

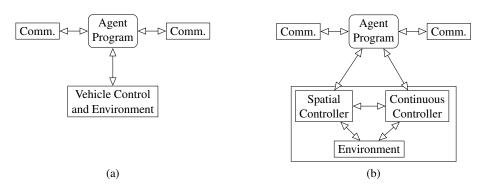

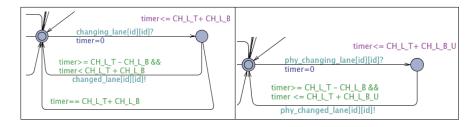

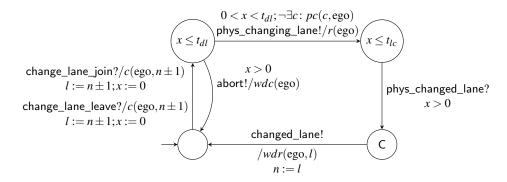

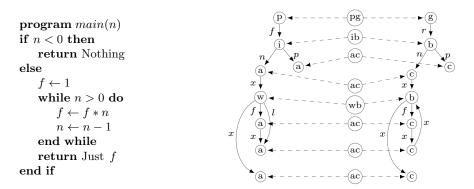

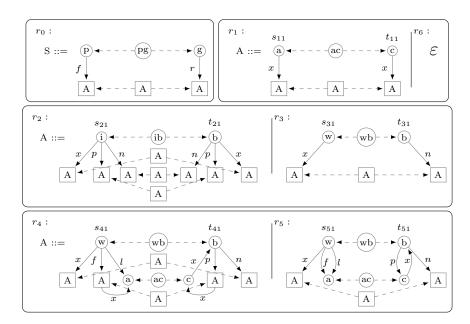

| SSLAF14-2       [42,40]       RTS       ×       6       14       2       4       -       √       ✓       Safety       ✓         ProdCons: 2-3       [31]       Prodcons.       √       5       5       6       0       L/U       √       ×       Reach.       ✓         train-AHV93       [3]       TGC       ×       3       3       6       0       L/U       ×       Safety         WFAS       [15]       Protocol       ×       3       4       2       0       -       √       ×       Safety       ✓         Industrial         accel:1       [27,10]       PTPM       √       2       2       3       0       -       √       ×       PTPM         accel:10       [27,10]       PTPM       √       2       2       3       0       -       √       ×       PTPM       1         BRP       [23]       Protocol       ×       6       7       2       12       -       √       ×       Safety       24         FMTV:1A1       [39]       RTS       ×       3       3       3       7       -                                                                                                                                                             | -3tasks:100-2 |